RTD(Resistance Temperature Detector)는 높은 정확도와 장기 안정성 덕분에 산업 및 계측 분야에서 가장 널리 사용되는 온도 센서 중 하나이다. 그러나 RTD 측정 회로는 리드 저항, 자체 발열, 전류원 불일치, EMI 등 다양한 요인에 의해 쉽게 정확도가 저하될 수 있다. 따라서 RTD의 이론적 특성을 이해하는 것만으로는 충분하지 않으며, 실제 회로 수준에서 발생하는 오차 요인을 정량적으로 분석하고 최적의 설계 방안을 찾는 것이 핵심 과제이다.

본 문서는 Texas Instruments의 24비트 ADC인 ADS124S08과 PT100 RTD를 기반으로, 대표적인 회로 토폴로지(2선식, 3선식, 4선식)를 비교·분석한다. 단순 나열식 가이드와 달리, 본 문서는 각 토폴로지의 오차 메커니즘을 정량적으로 평가하고, IDAC 전류, 기준 저항, PGA 이득 등 주요 설계 변수가 시스템 정확도에 미치는 영향을 체계적으로 제시한다. 이를 통해 설계자는 목표 정확도(<0.2°C) 달성을 위한 회로 구조 선택과 최적화 방법을 명확히 이해할 수 있다.

Keywords : RTD, 온도센서, 저항온도검출기, 정밀측정, 회로설계, 아날로그회로, TI, ADS124S08, 데이터시트, 센서인터페이스, RTD sensor, Temperature measurement, Precision circuit design, Ratiometric measurement, PT100, PT1000, Analog design, SPI ADC

1. RTD 센서 물리적 모델과 한계

1.1 CVD 방정식과 저항-온도 특성

RTD는 온도에 따라 저항이 변화하는 금속(주로 백금)을 사용한다. PT100(0°C에서 100Ω)과 PT1000(1000Ω)은 산업 표준이며, 저항-온도 관계는 Callendar-Van Dusen(CVD) 방정식으로 정의된다:

계산 예시: PT100, \( T = 100^\circ C \):

- \( R_{RTD} = 100 \cdot [1 + 3.9083 \times 10^{-3} \cdot 100 - 5.775 \times 10^{-7} \cdot 100^2] \approx 138.51\Omega \)

- 감도: \( \frac{\Delta R}{\Delta T} \approx 0.385\Omega/^\circ C \).

- PT1000: \( R_{RTD} \approx 1385.1\Omega \), 감도 3.85Ω/°C.

1.2 감도, 선형성, 자체 발열 한계

- 감도: PT100은 0.385Ω/°C, PT1000은 3.85Ω/°C. 높은 저항(PT1000)은 저전류로 SNR 개선.

- 선형성: CVD 방정식의 2차/3차 항으로 비선형 보정. 0~100°C에서 근사 선형.

- 자체 발열: 전류에 의한 발열, \( \Delta T = \frac{I^2 \cdot R_{RTD}}{E} \), E=2.5~65mW/°C.

계산 예시: PT100, IDAC=500μA, \( R_{RTD} = 138.5\Omega \):

- \( \Delta T = \frac{(0.0005)^2 \cdot 138.5}{2.5} \approx 0.014^\circ C \).

- IDAC=1mA: \( \Delta T \approx 0.055^\circ C \), 목표(<0.2°C)에 영향.

- 센서 오차: PT100은 수십 ppm/°C 오차(IEC-60751 Class A: ±0.15°C@0°C). 전자회로 오차는 이보다 작아야 함(<0.1°C).

1.3 한계와 설계 목표

RTD 자체는 고정밀이나, 리드 저항(0.5Ω → 1.3°C), 자체 발열, EMI로 정확도 저하. 설계 목표는 총 오차 <0.2°C 유지, ADC(24비트)와 ratiometric 측정 활용.

2. 고정밀 RTD 측정의 기본 프레임워크

2.1 Ratiometric 측정 원리

Ratiometric 측정은 IDAC로 RTD와 기준 저항(R_REF)을 구동, ADC가 \( V_{RTD}/V_{REF} \)를 측정해 드리프트 취소:

계산 예시: \( R_{RTD} = 138.5\Omega \), \( R_{REF} = 1620\Omega \), Gain=4, 3-Wire:

- \( Code = 4,194,304 \cdot 4 \cdot \frac{138.5}{1620} \approx 1,434,000 \)

- \( R_{RTD} = 1620 \cdot \frac{1,434,000}{4,194,304 \cdot 4} \approx 138.5\Omega \)

2.2 ADC 해상도 vs 온도 해상도

ADS124S08(24비트, ±2^23 풀스케일), PT100(0.385Ω/°C):

- 입력 범위: AVDD=3.3V, Gain=4, \( V_{IN} = \pm 0.825V \).

- LSB: \( \frac{2 \cdot 0.825}{2^{24}} \approx 0.098\mu V \).

- 온도 해상도: IDAC=500μA, \( V_{RTD} = 0.0005 \cdot 138.5 = 69.25mV \), \( \frac{0.098\mu V}{0.0005 \cdot 0.385} \approx 0.0005^\circ C \).

- 실제: ADC 노이즈(0.5μVrms) → \( \frac{0.5\mu V}{0.1925mV/^\circ C} \approx 0.0026^\circ C \).

2.3 기준 저항, IDAC, PCB 영향

- R_REF: 1620Ω, 0.01%, 5ppm/°C → 드리프트 0.021°C/°C.

- IDAC: 250~500μA, 0.02% 매칭(ADS124S08) → 3-Wire에서 0.01°C 오류.

- PCB: 누설 전류(1μA → 0.1°C), EMI로 입력 왜곡. 트위스트 페어, 스타 접지 필수.

3. 회로 토폴로지별 심층 분석

3.1 2-Wire RTD, Low-Side Reference

Path : IDAC1(AIN0) → RTD(Lead1-2) → R_REF → AVSS. 입력: AIN1-AIN2.

- 공식:

\[ V_{IN} = I_{IDAC1} \cdot (R_{RTD} + R_{LEAD}), \quad V_{REF} = I_{IDAC1} \cdot R_{REF} \] \[ Code = 2^{23} \cdot Gain \cdot \frac{R_{RTD} + R_{LEAD}}{R_{REF}} \]계산 예시: IDAC1=500μA, \( R_{RTD} = 138.5\Omega \), \( R_{LEAD} = 0.5\Omega \), \( R_{REF} = 1620\Omega \), Gain=4.

- \( V_{IN} = 0.0005 \cdot (138.5 + 0.5) = 0.0695V \)

- \( Code \approx 2,882,600 \), 오류 ≈ 1.3°C

- 오차 분석: 리드 저항(0.5Ω → 1.3°C, 65% of error budget), 누설(1μA → 0.36°C).

- 장단점: 단순, 저비용, 단점은 리드 오류.

- 설계 팁: 리드 <0.1Ω, RC 필터(1kΩ, 100nF).

3.2 2-Wire RTD, High-Side Reference

Path: IDAC1(AIN0) → R_REF → RTD → R_BIAS → AVSS.

- 공식: 동일 (3.1).

\[ V_{AIN0} = I_{IDAC1} \cdot (R_{REF} + R_{RTD} + R_{BIAS} + R_{LEAD}) \]계산 예시: R_BIAS=500Ω, \( R_{LEAD} = 0.5\Omega \).

- \( V_{AIN0} = 0.0005 \cdot (1620 + 138.5 + 500 + 0.5) = 1.0645V \)

- 오차 분석: 리드(1.3°C), R_BIAS 노이즈(3nV/√Hz).

- 장단점: 간단, 단점은 기준 전압, R_BIAS 노이즈.

- 설계 팁: R_BIAS <500Ω, 준수 확인 (AVDD-0.2V).

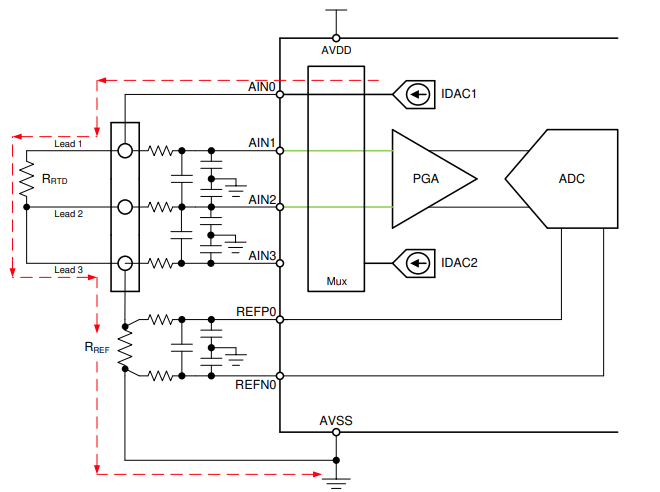

3.3 3-Wire RTD, Low-Side Reference

Path: IDAC1(AIN0, Lead1), IDAC2(AIN3, Lead2), R_REF(Lead3 via AVSS).

- 공식:

\[ V_{IN} = I_{IDAC} \cdot (R_{RTD} + R_{LEAD1} - R_{LEAD2}), \quad V_{REF} = 2 \cdot I_{IDAC} \cdot R_{REF} \] \[ Code = 2^{22} \cdot Gain \cdot \frac{R_{RTD} + \Delta R_{LEAD}}{R_{REF}} \]계산 예시: \( \Delta R_{LEAD} = 0.1\Omega \):

- \( Code \approx 1,434,000 \), 오류 ≈ 0.26°C

- 오차 분석: IDAC 불일치(1% → 0.5°C), 리드 불균형(0.26°C).

- 장단점: 리드 보상, 산업 표준, 단점은 IDAC 매칭.

- Chopping: IDAC1/2 교차로 불일치 제거.

- 설계 팁: Chopping(2ms), 트위스트 페어.

3.4 3-Wire RTD, Low-Side Reference, 단일 IDAC

Path: IDAC1(AIN0, Lead1), MEAS1(AIN1-AIN2), MEAS2(AIN2-AIN3).

- 공식:

\[ Code1 = 2^{23} \cdot Gain \cdot \frac{R_{RTD} + R_{LEAD1}}{R_{REF}}, \quad Code2 = 2^{23} \cdot Gain \cdot \frac{R_{LEAD3}}{R_{REF}} \] \[ R_{RTD} = R_{REF} \cdot \frac{Code1 - Code2}{2^{23} \cdot Gain} \]계산 예시: \( R_{RTD} = 138.5\Omega \), R_LEAD1=0.5Ω, R_LEAD3=0.5Ω, \( R_{REF} = 1620\Omega \), Gain=4.

- \( Code1 \approx 2,882,600 \), \( Code2 \approx 10,300 \)

- \( R_{RTD} \approx 138.5\Omega \)

- 오차 분석: 리드 불균형(0.26°C), MUX 정착(20μs → 0.05°C).

- 장단점: 단일 IDAC, 단점은 정착 지연.

- 설계 팁: RC 필터(1kΩ, 100nF), MUX 지연 20μs.

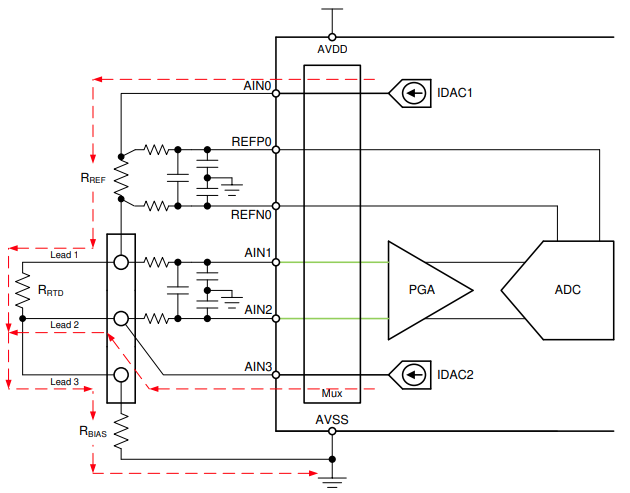

3.5 3-Wire RTD, High-Side Reference

Path: IDAC1(R_REF), IDAC2(Lead2), R_BIAS → AVSS.

- 공식: 동일 (3.1).

- 오차 분석: R_BIAS 노이즈(3nV/√Hz → 0.015°C).

- 장단점: IDAC 불일치 영향 적음, 단점은 R_BIAS.

- 설계 팁: R_BIAS <500Ω.

3.6 4-Wire RTD, Low-Side Reference

Path: IDAC1(Lead1), 입력 AIN1-AIN2(Lead2-3), R_REF(Lead4).

- 공식: 동일 (3.1).

- 오차 분석: 누설(1μA → 0.1°C), ADC 노이즈(0.0026°C).

- 장단점: 리드 저항 무시, 단점은 비용.

- 설계 팁: 켈빈 연결, EMI 쉴드.

3.7 Two Series 2-Wire RTD

Path: IDAC1(AIN0) → RTD1 → RTD2 → R_REF → AVSS. 입력: AIN1-AIN2 (RTD1), AIN2-AIN3 (RTD2).

상세 분석

- 동작 원리: 단일 IDAC로 두 RTD 직렬 구동, MUX로 개별 측정. Ratiometric 측정으로 드리프트 취소.

- 공식:

\[ V_{IN1} = I_{IDAC1} \cdot (R_{RTD1} + R_{LEAD1-2}), \quad V_{IN2} = I_{IDAC1} \cdot (R_{RTD2} + R_{LEAD3-4}) \] \[ V_{REF} = I_{IDAC1} \cdot R_{REF}, \quad Code1 = 2^{23} \cdot Gain \cdot \frac{R_{RTD1} + R_{LEAD1-2}}{R_{REF}} \]계산 예시: IDAC1=250μA, \( R_{RTD1} = R_{RTD2} = 138.5\Omega \), \( R_{LEAD} = 0.5\Omega \), \( R_{REF} = 1620\Omega \), Gain=4.

- \( V_{IN1} = 0.00025 \cdot (138.5 + 0.5) = 0.03475V \)

- \( V_{REF} = 0.00025 \cdot 1620 = 0.405V \)

- \( Code1 \approx 2,881,200 \), 오류 ≈ 1.3°C/RTD

- 오차 분석:

- 리드 저항: 0.5Ω → 1.3°C/RTD (65% of error budget).

- MUX 정착: 20μs → 0.05°C.

- 누설 전류: 1μA → 0.36°C.

- 장단점:

- 장점: 단일 IDAC, 간단한 배선.

- 단점: 리드 저항 오류, 기준 전압 증가 (\( V_{AIN0} = I_{IDAC1} \cdot (R_{RTD1} + R_{RTD2} + R_{REF} + R_{LEAD}) \)).

- 설계 팁: 리드 <0.1Ω, RC 필터(1kΩ, 100nF), MUX 정착 시간 20μs 이상.

3.8 Two Series 4-Wire RTD

Path: IDAC1(Lead1, RTD1), 입력 AIN1-AIN2(Lead2-3, RTD1), AIN3-AIN4(Lead6-7, RTD2), R_REF(Lead4).

상세 분석

- 동작 원리: 각 RTD에 4-Wire 켈빈 연결, MUX로 순차 측정. 리드 저항 무시.

- 공식:

\[ V_{IN1} = I_{IDAC1} \cdot R_{RTD1}, \quad V_{REF} = I_{IDAC1} \cdot R_{REF} \] \[ Code1 = 2^{23} \cdot Gain \cdot \frac{R_{RTD1}}{R_{REF}} \]계산 예시: IDAC1=250μA, \( R_{RTD1} = 138.5\Omega \), \( R_{REF} = 1620\Omega \), Gain=4.

- \( V_{IN1} = 0.00025 \cdot 138.5 = 0.034625V \)

- \( Code1 \approx 2,860,800 \), 오류 ≈ 0°C (리드 무시)

- 오차 분석:

- 누설 전류: 1μA → 0.1°C.

- ADC 노이즈: 0.5μVrms → 0.0026°C.

- MUX 정착: 0.05°C.

- 장단점:

- 장점: 최고 정확도, 리드 저항 무시.

- 단점: 8핀 배선, 높은 비용.

- 설계 팁: 켈빈 연결, EMI 쉴드, MUX 지연 20μs.

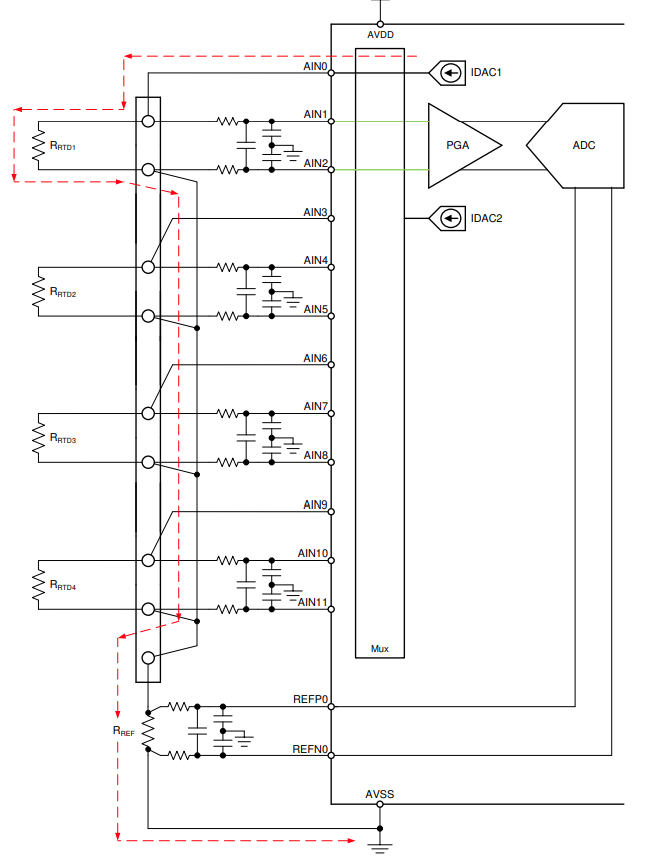

3.9 Multiple 2-Wire RTD

Path: IDAC1(AIN0), 4 RTD 병렬(MUX: AIN1-AIN2, AIN3-AIN4, ...), R_REF → AVSS.

상세 분석

- 동작 원리: 단일 IDAC, MUX로 RTD 순차 선택. 각 RTD는 2-Wire.

- 공식: 동일 (3.1).

계산 예시: 4 RTD, \( R_{RTD} = 138.5\Omega \), \( R_{LEAD} = 0.5\Omega \).

- \( Code \approx 2,882,600/RTD \), 리드 오류 ≈ 1.3°C.

- 오차 분석:

- 리드 저항: 1.3°C/RTD.

- MUX 정착: 0.05°C.

- 누설: 0.36°C.

- 장단점:

- 장점: 저비용, 배선 간단(2핀/RTD).

- 단점: 리드 오류, MUX 지연.

- 설계 팁: 리드 <0.1Ω, RC 필터, MUX 지연 20μs.

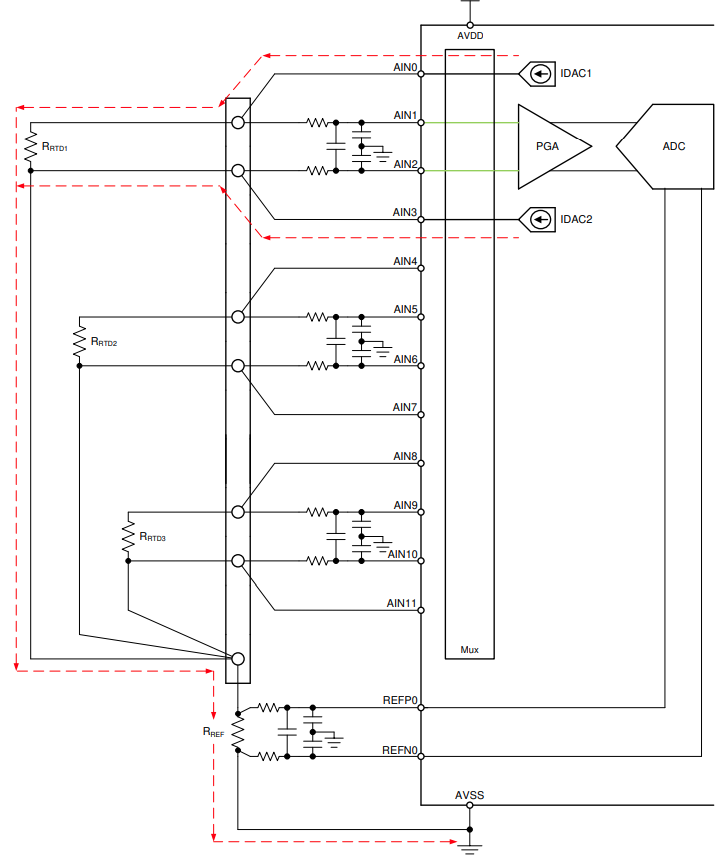

3.10 Multiple 3-Wire RTD

Path: IDAC1(AIN0, Lead1), IDAC2(AIN5, Lead2), 3 RTD(MUX: AIN1-AIN2, AIN3-AIN4, ...), R_REF(Lead3).

상세 분석

- 동작 원리: 각 RTD에 3-Wire 연결, IDAC1/2로 리드 보상, MUX로 순차 측정.

- 공식: 동일 (3.3).

계산 예시: 3 RTD, \( R_{RTD} = 138.5\Omega \), \( \Delta R_{LEAD} = 0.1\Omega \).

- \( Code \approx 1,434,000/RTD \), 리드 불균형 ≈ 0.26°C.

- 오차 분석:

- IDAC 불일치: 1% → 0.5°C (chopping 제거).

- 리드 불균형: 0.26°C.

- MUX 정착: 0.05°C.

- 장단점:

- 장점: 리드 보상, 산업 표준.

- 단점: IDAC 매칭, MUX 지연.

- 설계 팁: Chopping(2ms), RC 필터, 트위스트 페어.

3.11 Multiple 4-Wire RTD

Path: IDAC1(Lead1), 4 RTD(MUX: AIN1-AIN2, AIN3-AIN4, ...), R_REF(Lead4).

상세 분석

- 동작 원리: 각 RTD에 4-Wire 켈빈 연결, MUX로 순차 측정.

- 공식: 동일 (3.1).

계산 예시: 4 RTD, \( R_{RTD} = 138.5\Omega \).

- \( Code \approx 2,860,800/RTD \), 리드 오류 0°C.

- 오차 분석:

- 누설: 0.1°C.

- MUX 정착: 0.05°C.

- ADC 노이즈: 0.0026°C.

- 장단점:

- 장점: 최고 정확도, 리드 무시.

- 단점: 4핀/RTD, 높은 비용.

- 설계 팁: 켈빈 연결, EMI 쉴드, MUX 지연 20μs.

3.12 범용 RTD 인터페이스, Low-Side Reference

Path: IDAC1/2(선택 가능), 5핀 인터페이스(AIN0~AIN4), R_REF → AVSS. MUX/IDAC 동적 설정으로 2/3/4-Wire 호환.

상세 분석

- 동작 원리: 단일 회로로 모든 RTD 유형 지원. 소프트웨어로 MUX/IDAC 설정 변경.

- 공식:

\[ \text{2-Wire: } Code = 2^{23} \cdot Gain \cdot \frac{R_{RTD} + R_{LEAD}}{R_{REF}} \] \[ \text{3-Wire: } Code = 2^{22} \cdot Gain \cdot \frac{R_{RTD} + \Delta R_{LEAD}}{R_{REF}} \] \[ \text{4-Wire: } Code = 2^{23} \cdot Gain \cdot \frac{R_{RTD}}{R_{REF}} \]계산 예시: 3-Wire, \( R_{RTD} = 138.5\Omega \), \( \Delta R_{LEAD} = 0.1\Omega \).

- \( Code \approx 1,434,000 \), 오류 ≈ 0.26°C.

- 오차 분석:

- 2-Wire: 리드(1.3°C).

- 3-Wire: IDAC 불일치(0.5°C), 리드 불균형(0.26°C).

- 4-Wire: 누설(0.1°C).

- MUX 정착: 0.05°C.

- 장단점:

- 장점: 유연성, 단일 회로로 다중 RTD 지원.

- 단점: 설정 복잡, 소프트웨어 부담.

- 설계 팁: 설정 검증 소프트웨어, RC 필터, 5핀 인터페이스 최적화.

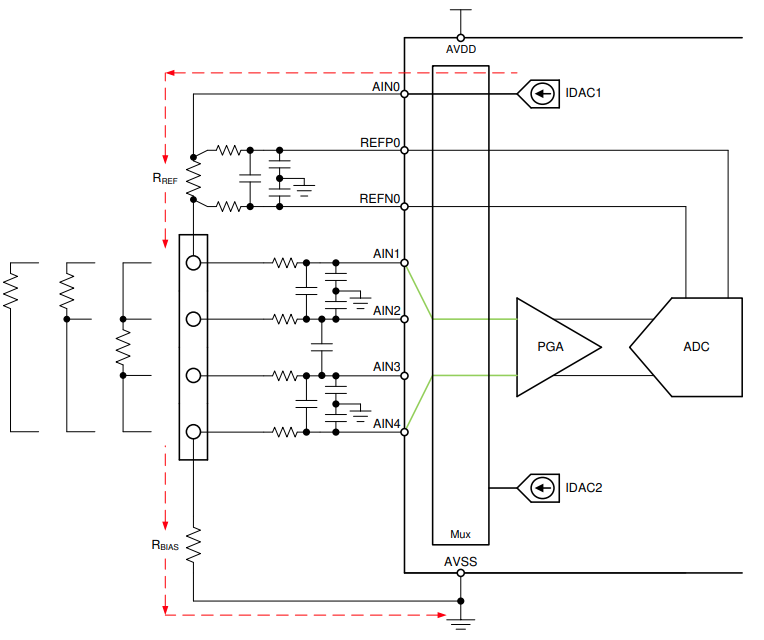

3.13 범용 RTD 인터페이스, High-Side Reference

Path: IDAC1/2(선택 가능), R_REF → RTD → R_BIAS → AVSS, 5핀 인터페이스.

상세 분석

- 동작 원리: High-Side R_REF로 기준 전압 관리, 2/3/4-Wire 동적 지원.

- 공식: 동일 (3.12).

계산 예시: 4-Wire, \( R_{RTD} = 138.5\Omega \).

- \( V_{AIN0} = 0.00025 \cdot (1620 + 138.5) = 0.439625V \)

- \( Code \approx 2,860,800 \).

- 오차 분석:

- R_BIAS 노이즈: 3nV/√Hz → 0.015°C.

- MUX 정착: 0.05°C.

- 장단점:

- 장점: 유연성, High-Side 호환.

- 단점: R_BIAS 노이즈, 기준 전압 관리.

- 설계 팁: R_BIAS <500Ω, 준수 확인, 소프트웨어 설정 최적화.

4. 설계 변수 최적화

4.1 IDAC 전류

Trade-off: 자체 발열 vs SNR.

- 250μA: \( \Delta T \approx 0.0035^\circ C \), SNR 낮음.

- 500μA: \( \Delta T \approx 0.014^\circ C \), SNR 적절.

- 권장: 250~500μA, 펄스 구동(10ms).

4.2 기준 저항 값

선정 기준: AVDD=3.3V 내 준수.

- \( V_{REF} = I_{IDAC} \cdot R_{REF} \leq 2.5V \).

- \( R_{REF} = 1620\Omega \), IDAC=500μA → \( V_{REF} = 0.81V \).

- 0.01%, 5ppm/°C 권장.

4.3 PGA 이득

관계: 입력 범위 vs ADC 노이즈.

- Gain=4: \( V_{IN} \leq 0.825V \), 노이즈 0.5μVrms → 0.0026°C.

- Gain=16: 노이즈 증폭, 클리핑 위험.

4.4 샘플링 속도

Trade-off: 노이즈 vs 지터.

- 20SPS: 노이즈 0.5μVrms, 안정.

- 2000SPS: 노이즈 1.2μVrms, 지터 증가.

5. 실무 고려사항 (System-Level)

5.1 다채널 RTD

MUX 정착 시간: 20μs → 0.05°C 오류. RC 필터(1kΩ, 100nF)로 안정화.

5.2 EMI/노이즈 대응

- RC 필터: 1kΩ, 100nF (cutoff 1.6kHz).

- PCB: 트위스트 페어, 스타 접지, 쉴드.

5.3 MCU 펌웨어 보정

- CVD 룩업 테이블(1000점) 또는 다항식 근사.

- 이동 평균(10샘플)으로 노이즈 감소.

5.4 장기 안정성

- R_REF TCR: 5ppm/°C → 0.021°C/°C.

- IDAC 드리프트: 0.005%/°C.

- ADC 오프셋: 0.1μV/°C.

6. 결론

본 문서에서는 RTD의 물리적 특성과 오차 요인을 기반으로, 대표적인 회로 토폴로지(2-Wire, 3-Wire, 4-Wire)를 정량적으로 비교·분석하였다. 2선식은 단순하지만 리드 저항에 의해 수 °C 수준의 오류가 발생할 수 있으며, 4선식은 최고 정확도를 제공하지만 비용과 복잡도가 크다. 이에 따라 산업 현장에서는 3선식 Low-Side Reference 방식이 비용 효율과 정확도 사이의 최적 절충안으로 널리 사용된다.

설계 최적화를 위해서는 IDAC 전류를 250~500 μA 범위로 설정하여 자체 발열을 억제하고, 저 TCR 고정밀 기준 저항(예: 1620 Ω, 0.01%)을 채택하는 것이 필수적이다. 또한, ADC의 샘플링 속도와 PGA 이득을 응용 환경에 맞추어 조정함으로써 시스템 노이즈를 최소화할 수 있다.

결론적으로, 본 문서에서 제시한 원칙과 분석을 적용하면 일반 산업 응용에서는 ±0.2°C 이하, 연구 및 계측 분야에서는 ±0.05°C 수준의 온도 측정 정확도를 달성할 수 있다.

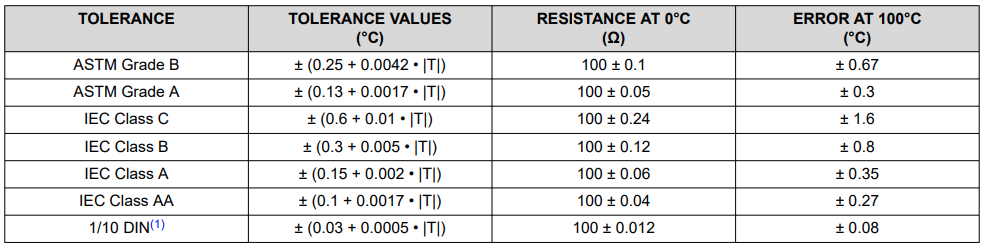

6.1 오류 예산 표

| 오차 요인 | 2-Wire (°C) | 3-Wire (°C) | 4-Wire (°C) | Multi 2-Wire (°C) | Multi 3-Wire (°C) | Multi 4-Wire (°C) | Universal (°C) |

| 리드 저항 | 1.3 | 0.26 | 0 | 1.3 | 0.26 | 0 | 0~1.3 |

| IDAC 불일치 | 0 | 0.5 (0 with chopping) | 0 | 0 | 0.5 (0 with chopping) | 0 | 0~0.5 |

| 자체 발열 | 0.014 | 0.014 | 0.014 | 0.014 | 0.014 | 0.014 | 0.014 |

| 누설 전류 | 0.36 | 0.1 | 0.1 | 0.36 | 0.1 | 0.1 | 0.1~0.36 |

| ADC 노이즈 | 0.0026 | 0.0026 | 0.0026 | 0.0026 | 0.0026 | 0.0026 | 0.0026 |

| R_REF 드리프트 | 0.021 | 0.021 | 0.021 | 0.021 | 0.021 | 0.021 | 0.021 |

| MUX 정착 | 0 | 0 | 0 | 0.05 | 0.05 | 0.05 | 0.05 |

| 총 오차 | 1.6976 | 0.1476 (chopping) | 0.1376 | 1.7476 | 0.1976 (chopping) | 0.1876 | 0.1876~1.7476 |

7. 예제 코드

아래 코드는 ADS124S08, Multiple 3-Wire Low-Side 회로 기준을 작성되었습니다.

#include <stdint.h>

#include <math.h>

#include "stm32f4xx.h"

#include "ads124s08.h"

// ADS124S08 레지스터

#define ADS124S08_REG_INPMUX 0x01

#define ADS124S08_REG_PGA 0x02

#define ADS124S08_REG_DATARATE 0x03

#define ADS124S08_REG_REF 0x04

#define ADS124S08_REG_IDAC 0x06

// CVD 상수 (PT100)

#define R0 100.0f

#define A 3.9083e-3f

#define B -5.775e-7f

#define NUM_RTD 3

void spi_write(uint8_t reg, uint8_t data);

uint32_t spi_read_adc(void);

void ads124s08_init(void) {

spi_write(ADS124S08_REG_PGA, 0x02); // Gain=4

spi_write(ADS124S08_REG_DATARATE, 0x04); // 20SPS

spi_write(ADS124S08_REG_REF, 0x00); // 외부 참조

}

float rtd_to_temperature(float r_rtd) {

float a = B, b = A, c = (1.0f - r_rtd / R0);

float discriminant = b * b - 4 * a * c;

if (discriminant < 0) return NAN;

return (-b + sqrtf(discriminant)) / (2 * a);

}

float measure_rtd(uint8_t rtd_idx) {

const float R_REF = 1620.0f, GAIN = 4.0f, SCALE = 4194304.0f;

uint8_t mux[] = {0x12, 0x34, 0x56}; // AINP/AINN: RTD1(1-2), RTD2(3-4), RTD3(5-6)

uint32_t code1, code2;

spi_write(ADS124S08_REG_INPMUX, mux[rtd_idx]);

spi_write(ADS124S08_REG_IDAC, 0x54); // IDAC1=AIN0, IDAC2=AIN5

code1 = spi_read_adc();

spi_write(ADS124S08_REG_IDAC, 0x45); // Chopping

code2 = spi_read_adc();

float code_avg = (code1 + code2) / 2.0f;

float r_rtd = R_REF * (code_avg / (SCALE * GAIN));

return rtd_to_temperature(r_rtd);

}

int main(void) {

ads124s08_init();

float temperatures[NUM_RTD];

while (1) {

for (uint8_t i = 0; i < NUM_RTD; i++) {

temperatures[i] = measure_rtd(i);

}

for (volatile int i = 0; i < 1000000; i++);

}

}

Keywords : RTD, 온도센서, 저항온도검출기, 정밀측정, 회로설계, 아날로그회로, TI, ADS124S08, 데이터시트, 센서인터페이스, RTD sensor, Temperature measurement, Precision circuit design, Ratiometric measurement, PT100, PT1000, Analog design, SPI ADC

참고 자료

- Texas Instruments, “A Basic Guide to RTD Measurements (SBAA275A)”, Revised March 2023.

👉 PDF 보기 - Texas Instruments, “ADS124S08 24-Bit Low-Noise Delta-Sigma ADC with PGA and Voltage Reference – Datasheet”, 2018.

👉 제품 페이지 - Texas Instruments, “RTD Ratiometric Measurements and Filtering Using the ADS1148 (Application Note SBAA201)”, 2012.

👉 PDF 보기 - Analog Devices, “How to Select and Design the Best RTD Temperature Sensing System”, Analog Dialogue.

👉 문서 보기 - Luis Chioye, “Improve Noise Immunity On RTD Ratiometric Measurements”, Electronic Design, April 1, 2013.

👉 기사 보기

'Sensor > 온도센서(Temperature)' 카테고리의 다른 글

| Thermistor(써미스터) (0) | 2025.08.05 |

|---|---|

| RTD 온도 센서 보상 알고리즘 (RTD Temperature Sensor Compensation Algorithm) (0) | 2025.08.05 |

| RTD (측온저항체,Resistance Temperature Detector) (0) | 2025.08.04 |

| ThermoCouple(열전대) NIST 기반 보정 알고리즘 코드 구현 (0) | 2025.08.04 |

| Thermocouple(열전대) (0) | 2025.08.03 |

| Temperature Sensor(온도센서) 관련 전체 요약 (0) | 2025.08.03 |